Prof. Dr. Amir Moradi

Head of the Chair

Working area(s)

Contact

amir.moradi@tu-...

work +49 6151 16 25725

Work

S4|14 2.4.18

Mornewegstraße 30-32

64293

Darmstadt

Links

Curriculum Vitae

| Since 10/2023 |

W3 Professor for Implementation Security Department of Computer Science, Technische Universität Darmstadt, Germany |

| 8/2022 – 10/2023 |

W2 Professor for Implementation Security Faculty of Computer Science, Ruhr-Universität Bochum, Germany |

|

10/2021 – 8/2022 |

W2 Professor for IT-Security Institute of Computer Science, University of Cologne, Germany |

| 4/2021 – 10/2021 |

Extraordinary Professor (Außerplanmäßiger Professor) Faculty of Electrical Engineering and Information Sciences, Ruhr-Universität Bochum, Germany |

| 1/2020 – 10/2021 |

Academic Councilor (Akademischer Rat) Security Engineering, Ruhr-Universität Bochum, Germany |

| 2016 – 2019 |

Academic Councilor (Akademischer Rat) Embedded Security, Ruhr-Universität Bochum, Germany |

| 10/2015 – 4/2021 |

Faculty Member (Privatdozent) Faculty of Electrical Engineering and Information Sciences, Ruhr-Universität Bochum, Germany |

| 2015 |

Habilitation in Embedded Security (Advances in Side-Channel Security) Ruhr-Universität Bochum, Germany |

| 2009 – 2016 |

Post-Doctoral researcher Embedded Security, Ruhr-Universität Bochum, Germany |

| 2008 |

PhD in Computer Engineering Sharif University of Technology, Tehran, Iran |

| 2007 – 2008 |

Visiting PhD student Embedded Security, Ruhr-Universität Bochum, Germany |

| 2004 |

MSc in Computer Engineering Sharif University of Technology, Tehran, Iran |

| 2001 |

BSc in Computer Engineering Shahid Beheshti University, Tehran, Iran |

Research Topics

| Implementation Security |

| Side-Channel Analysis and Countermeasures |

| Fault-Injection Attacks and Countermeasures |

| Efficient Implementation of Cryptographic Primitives |

| Hardware Trojans |

| Applied Cryptography |

Profiles

Awards and Honors

| Highest number of publications at CHES 2024 with 7 papers |

| Distinguished Paper Award at IEEE S&P 2023 |

| Awarded by 100,000 € (1st place) in the 9th German IT Security Award 2022, announcement |

| Highest number of publications at CHES 2022 with 8 papers, announcement |

| Highest number of publications at CHES in one year for the entire history of CHES, with 10 publications at CHES 2021, announcement |

| Currently the 2nd prolific author of CHES |

| Distinguished Paper award at USENIX Security Symposium – USENIX 2020 |

| Best paper award at Conference on Cryptographic Hardware and Embedded Systems – CHES 2019 |

| Co-author of the Best Student-Paper Award at IEEE International Symposium on Hardware Oriented Security and Trust – HOST 2016 |

| Best Paper Award at International Workshop on Constructive Side-Channel Analysis and Secure Design – COSADE 2015 |

| Co-author of the Best Student-Paper Award at International Conference on Applied Cryptography and Network Security – ACNS 2014 |

| Nominated for the best paper award at Design, Automation & Test in Europe Conference & Exhibition – DATE 2018 |

| Nominated for the best paper award at Design, Automation & Test in Europe Conference & Exhibition – DATE 2017 |

| Nominated for the best paper award at Workshop on Cryptographic Hardware and Embedded Systems – CHES 2015 |

Program Committee / Editorial Board Membership

|

60+ memberships including CHES, EUROCRYPT, ASIACRYPT, FSE, INDOCRYPT, DATE, CARDIS, COSADE |

| PC co-chair of Smart Card Research and Advanced Application Conference (CARDIS 2014) |

| PC co-chair of International Workshop on Lightweight Cryptography for Security & Privacy (LightSec 2015) |

| PC co-chair of Cryptographic Hardware and Embedded Systems (CHES 2020) |

| Member of CHES Steering Committee, since 2019 |

| Member of CARDIS Steering Committee, 2014 – 2023 |

| Chair of the CHES Test of Time Award Committee, 2022 & 2023 |

| Associate Editor of International Journal of Applied Cryptography, 2011 – 2020 (IJACT) |

| Associate Editor of IEEE Transactions on Emerging Topics in Computing, 2019 – 2021 (IEEE-TETC) |

| Associate Editor of Journal of Cryptographic Engineering, 2019 – 2022 (JCEN) |

Selected Talks

| Statistical Tools Flavor Side-Channel Collision Attacks, EUROCRYPT 2012, April 17, Cambridge, UK. (talk) |

| Breaking the Bitstream Decryption of FPGAs, invited talk at ECRYPT II Summer School: Challenges in Security Engineering, 2012, September 5, Bochum, Germany |

| How Far Should Theory Be from Practice? Evaluation of a Countermeasure, CHES 2012, September 10, Leuven, Belgium |

| On the Simplicity of Converting Leakages from Multivariate to Univariate, CHES 2013, August 21, Santa Barbara, USA |

| Altera vs. Xilinx which one keeps your design hidden? rump session CHES 2013, August 22, Santa Barbara, USA |

| Side-Channel Countermeasures for Hardware: is There a Light at the End of the Tunnel? invited talk at Worcester Polytechnic Institute, 2013, September 11, Worcester, USA |

| Evaluation of Side-Channel Leakages through Statistical Moments invited talk at Bosch GmbH, 2014, March 13, Stuttgart, Germany |

| Side-Channel Leakage through Static Power Should We Care about in Practice? invited talk at NXP Semiconductors, 2014, April 22, Hamburg, Germany (+ CHES 2014, September 26, Busan, South Korea) |

| Early Propagation and Imbalanced Routing, How to Diminish in FPGAs, CHES 2014, September 26, Busan, South Korea |

| Physical Attacks, extracting the secrets from cryptographic devices, invited talk at Bauhaus-Universität Weimar, 2015, January 22, Weimar, Germany |

| Side-Channel Security Analysis of Ultra-Low-Power FRAM-based MCUs, COSADE 2015, April 14, Berlin, Germany |

| Hiding Higher-Order Leakages in Hardware invited talk at TI day, KU Leuven, Belgium |

| Leakage Assessment Methodology – a clear roadmap for side-channel evaluations, invited talk at Sharif University of Technology, 2015, August 29, Tehran, Iran |

| Improved Side-Channel Analysis Attacks on Xilinx Bitstream Encryption of 5, 6, and 7 Series, COSADE 2016, April 14, Graz, Austria |

| Masking as a Side-Channel Countermeasure in Hardware, invited tutorial at ISCISC 2016, September 6, Tehran, Iran |

| Moments-Correlating DPA, CCS 2016 Workshops (TIS), October 24, Vienna, Austria |

| Side-Channel Analysis Protection and Low-Latency in Action – case study of PRINCE and Midori, ASIACRYPT 2016, December 07, Hanio, Vietnam. (talk) |

| Bit-Sliding: A Generic Technique for Bit-Serial Implementations of SPN-based Primitives, CHES 2017, September 28, Taipei, Taiwan. (talk) |

| The First Thorough Side-Channel Hardware Trojan, ASIACRYPT 2017, December 05, Hong Kong, China. (talk) + at Theory of Implementation Security (TIS) Workshop 2018, January 09, Zurich, Switzerland |

| Exploring the Effect of Device Aging on Static Power Analysis Attacks, CHES 2019, August 28, Atlanta, USA. (talk) |

| How to Apply Threshold Implementation to any PUF Primitive, invited talk at Theory of Implementation Security (TIS) Workshop 2019, November 11, London, England |

| Threshold Implementation and Leakage Assessment, invited talk at Qualcomm, December 14, 2020 |

| Tools for Verification and Automatic Generation of Secure Hardware Circuits, invited talk at National Institute for Standard and Technology, USA, March 10, 2021 |

| Verification and Automatic Generation of Masked Hardware Designs, invited talk at Worcester Polytechnic Institute, USA, November 10, 2021 |

| Hardware Masking. Past, Present, and the Future, invited talk at Microsoft, December 8, 2021 |

| Automated Generation of Masked Hardware, CHES 2022, September 19, Leuven, Belgium. (talk) |

Finished PhDs

| 2016 | Oliver Mischke (jointly supervised with Tim Güneysu) |

| 2018 | Pascal Sasdrich (jointly supervised with Tim Güneysu) |

| 2018 | Tobias Schneider (jointly supervised with Tim Güneysu) |

| 2018 | Alexander Wild (jointly supervised with Tim Güneysu) |

| 2020 | Bastian Richter |

| 2020 | Shahram Rasoolzadeh |

| 2021 | Thorben Moos |

| 2022 | Anita Aghaie |

| 2023 | David Knichel |

| 2023 | Aein Rezaei Shahmirzadi |

| 2024 | Maik Ender (jointly supervised with Christof Paar) |

| 2025 | Nicolai Müller |

Funded DFG Projects

| NaSCA – Nano-Scale Side-Channel Analysis: Physical Security for Next-Generation CMOS ICs (DFG 2016-2020) |

| GreenSec – Security for Internet of Things with Low Energy and Low Power Consumption (DFG 2018-2021) |

| SuCCESS – SymmetriC CiphEr design with inherent phySical Security (DFG 2019-2023) |

| Aged but Fit – Long Lasting Security for Trusted Platforms (DFG 2020-2022) |

| SAUBER – phySicAlly secUre reconfiguraBlE platfoRm (DFG 2020-2024) |

| SecFShare – Secure Sharing of FPGAs in Clouds (DFG 2021-2024) |

| SSIMA – Scalable Side-Channel Immune Micro-Architecture (DFG 2024-2026) |

| MatSec – Maturing Physical Security Models in Realistic Scenarios (DFG 2026-2029) |

Funded EU Projects

| enCRYPTON – Twinning towards excellence for Privacy Enhancing Technologies leveraging Homomorphic Encryption (HORIZON-CSA 2022-2025) |

Funded BMBF Projects

| VeriSec – Computer-Assisted Integration and Verification of Masking in Cryptographic Implementations (BMBF 2017-2020) |

| SysKit – A Development Tool for Secure Communications in Industry 4.0 (BMBF 2017-2020) |

| mINDFUL – Intrusion Detection in Industry 4.0 via Fusion of Physical Channels using Artificial Intelligence (BMBF 2020-2023) |

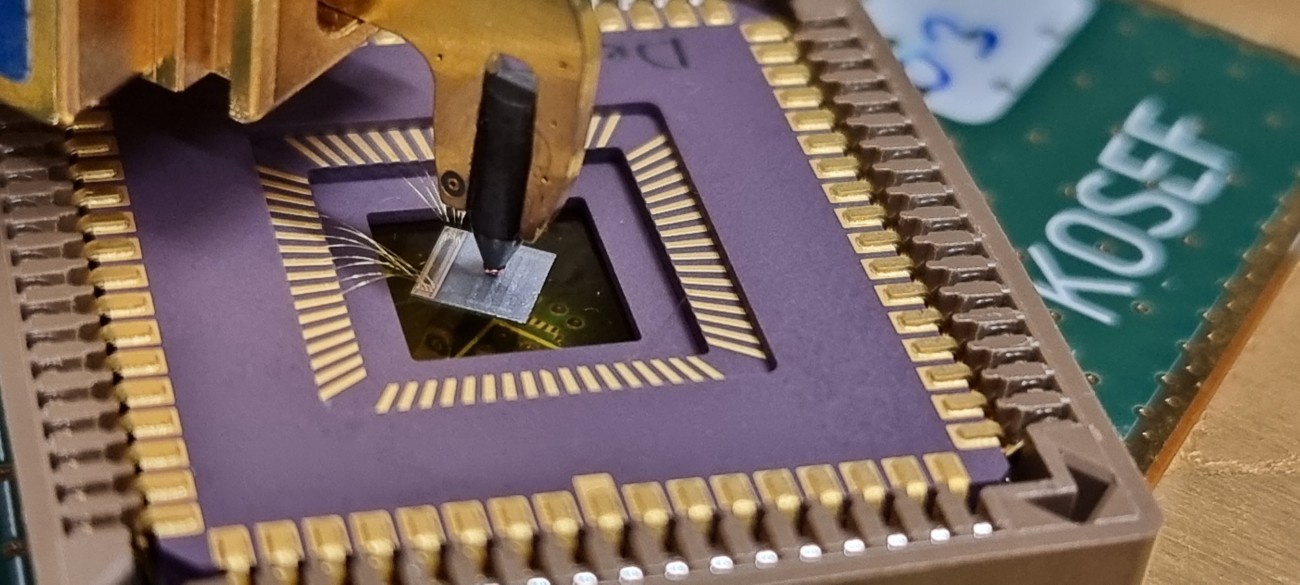

| KOSEF – Cost-optimized and Effective Protection against Electromagnetic Fault Injection to Ensure Data and Operational Reliability in loT Systems. (BMBF 2022-2025) |

| DevToSCA – Developer-Centric Tools for Side-Channel Analysis (BMBF 2022-2025) |

| ProPair – Context-based Trust Initialization of Telemedicine Micro Devices (BMBF 2022-2025) |